開発項目 「SIP (戦略的イノベーション創造プログラム) / 次世代パワーエレクトロニクス/SiC に関する拠点型共通基盤技術開発/SiC 次世代パワーエレクトロニクスの統合的研究 開発」 平成 26 年度~平成 28 年度

のうち平成26年度分中間年報

委託先名:独立行政法人産業技術総合研究所、国立大学法人京都大学、国立大学法人大阪大学、 一般財団法人電力中央研究所

# [記載項目]

# 1. 研究開発の内容及び成果等

本開発項目では、SiC パワーエレクトロニクスの普及と適用先拡大を目指した次世代技術として、①エピ成長やウエハ加工をも含めて革新的手法を取り入れた次世代 SiC ウエハ (基板) 作製技術、②低損失性・高耐圧性をより向上させる新規構造/プロセスを取り入れた次世代 SiC デバイス作製技術、③高電流密度デバイスを搭載したうえで小型軽量化と信頼性評価法確立を目指す次世代 SiC モジュール作製技術を対象に、一貫した統合的研究開発を当該分野における産学官の有力研究機関の研究者を結集して行う。

プロジェクト初年度である本年度は、上記3研究開発課題について研究開発を行い以下のような成果を 得た。

### ①次世代 SiC ウェハの技術開発

#### ①-(1) 伝導度制御技術開発

平成 26 年度は、4H-SiC バルク単結晶成長における低抵抗化および高純度化の二つの伝導度制御技術開発方針に従い、つくば拠点(昇華法、溶液法)および電中研拠点(ガス法)において各結晶成長法の現状技術レベルの把握と窒素(N)とアルミニウム(A1)の高濃度コドーピング法をベースとした不純物制御技術の開発に着手した。

昇華法の研究からは N-A1 (濃度) の値が  $3\times10^{19} \mathrm{cm}^{-3}$  を上回る試料では概して  $10\mathrm{m}\,\Omega\,\mathrm{cm}$  を下回る条件となることが確認できた。また、積層欠陥を抑制するには A1 濃度が  $1\times10^{19} \mathrm{cm}^{-3}$  以上のコドーピング条件が必要であることが判明した。次年度はこれらの知見を元に  $3\mathrm{inchx}10\mathrm{mmt}$  バルク結晶の作製、p 型低抵抗結晶成長の低抵抗化と高成長速度化を実施する計画である。

溶液法を用いたバルク成長では、n型結晶育成でマクロ欠陥発生が顕在化する問題に対し、成長るつぼ構造見直しと、計算機シミュレーションにより、成長面内の温度勾配を 0.5% /cm 以下で均熱化させることで結晶成長面の改善を達成した。キャリア濃度は  $8\times10^{18}$  cm $^{-3}$   $\sim1\times10^{19}$  cm $^{-3}$  程度の高濃度で制御されている。p型成長は A1 ドーパントの効果で高品質かつ低抵抗の結晶を得やすい成長条件を持つが、n型成長実験と同様の均熱化対策を導入することで平均比抵抗約  $60m\Omega$  cm の 3 inch 低抵抗 p型 SiC バルク単結晶を得た。再委託先の名古屋大学では、溶液法において見いだした貫通転位変換による低転位化技術を n型および p型 SiC 成長技術に導入し、その効果を検証した。その結果、N および A1 がドーピングされた SiC 結晶中でも貫通転位が基底面転位に変換され、結晶外へ追い出すことで低欠陥化が可能であることが明らかとなった。また、口径制御に必須の過飽和度分布制御を検討するシミュレーション技術を確立した。次年度、溶液法においては、名古屋大学の知見との融合により伝導度制御と高品質化の両立を目指す。

また、電中研拠点では、ガス法での高濃度ドーピング実験を行うためのガス供給システムを設計するとともに、エピ成長によって高濃度の窒素ドーピングを行ったサンプルを用意し、フォトルミネッセンスイメージングや放射光 X 線トポグラフィを用いて積層欠陥の生成の有無、生成様相を明らかにした。同時に、フォトルミネッセンスイメージングによるダブルショックレー型積層欠陥の検出手法を得た。

一方、活性層に相当する低濃度 n 型単結晶をバルク CVD 法で成長する研究では、(0001)Si 面 と(000-1)C 面 (共に off 角なし) における成長の多形安定性を調査した。実験の結果、4H 多型は (000-1)C 面でのみで得られることが判明した。また、活性層の薄化ウェハ加工の破損リスクを回避する技術を検討するためウェハ抗折力試験など着手し、薄化研削では 4 インチウェハで 150  $\mu$  m 厚を達成した。次年度は CMP 工程までの加工特性把握と加工高速化を併せて実施し、デバイス 開発用ウェハ (250  $\mu$  mt) を試作する計画である。

再委託先の大阪電通大では、未知である高濃度ドープ SiC の伝導機構の解明を進めるため、ホール効果の交流電圧(10 Hz~100 kHz)に対するインピーダンスの温度依存性を測定する設備を構築中である。本年度は室温のみでの測定・考察となった。バンド伝導を示す高濃度コドープ n型 SiC のインピーダンスの周波数依存性は理論通り見られなかったが、ホッピング伝導と考えられるホール素子のインピーダンスの絶対値と位相の周波数依存性を磁場中で測定すると、磁場印加でインピーダンスの絶対値の増加(位相変化なし)や、それら周波数依存性(10 kHz まで位相は負)が確認された。これらを踏まえ今後、高濃度ドープ SiC の低温時のホッピング伝導化現象の解析を進める。

# ①-(2) 高耐圧化対応技術開発

平成 26 年度は、順方向劣化の抑制を目的としたライフタイム制御技術、転位変換による基底面転位密度低減技術、250 μm 超の高品質厚膜成長に必要な低欠陥化、外形制御技術の開発を Si 面、C 面の両面極性において実施するための環境整備と現状把握を中心に実施した。

ライフタイム制御についてはつくば拠点と電中研拠点と共同で Si 面における高濃度ドーピングによるライフタイム制御の試みを開始した。転位変換による基底面転位密度低減においては現状の転換効率の確認、基本的な成長パラメーター依存性、CVD 装置依存性の調査のため、試験用サンプル作製を行い現在評価中である。今後は、転換効率に影響を与えるパラメーターの調査から、転換のメカニズムを明らかにし、装置に依らない普遍的な転位変換技術の開発へと繋げていく。

一方、京大拠点では、ドーピング密度の異なる厚膜 SiC エピ成長層(n 型:  $10^{14}\sim10^{19}$  cm<sup>-3</sup>、p 型:  $10^{14}\sim10^{19}$  cm<sup>-3</sup>)を作製し、そのキャリア寿命(室温)のドーピング密度依存性を評価した。n 型、p 型共に低濃度ドープ結晶のキャリア寿命は as-grown で  $1\sim2$   $\mu$ s であるが、ドーピング密度の増大と共に急激に低下し、ドーピング密度が  $10^{18}$  cm<sup>-3</sup> を越えると 50  $\mu$ s 以下に低下することが分かった。また、高温熱処理による  $\mathbf{Z}_{1/2}$  センター生成を活用したキャリア寿命制御に取り組んだ。 $\mathbf{M}$  型厚膜成長層を準備し、( $\mathbf{M}$  )成長直後(as-grown)、( $\mathbf{M}$  )、( $\mathbf{M}$  )前述の試料に熱処理( $\mathbf{M}$  ないてキャリア寿命を評価した。 as-grown 結晶で約  $\mathbf{M}$  2  $\mathbf{M}$  であったキャリア寿命が熱酸化処理により  $\mathbf{M}$  27  $\mathbf{M}$  3 に向上した。この試料に高温  $\mathbf{M}$  4 なった。高温  $\mathbf{M}$  4 なった。高温  $\mathbf{M}$  5  $\mathbf{M}$  6  $\mathbf{M}$  7  $\mathbf{M}$  7  $\mathbf{M}$  8  $\mathbf{M}$  9  $\mathbf{M}$  9  $\mathbf{M}$  1  $\mathbf{M}$  2  $\mathbf{M}$  1  $\mathbf{M}$  2  $\mathbf{M}$  3  $\mathbf{M}$  2  $\mathbf{M}$  2  $\mathbf{M}$  3  $\mathbf{M}$  4  $\mathbf{M}$  2  $\mathbf{M}$  3  $\mathbf{M}$  4  $\mathbf{M}$  4  $\mathbf{M}$  5  $\mathbf{M}$  5  $\mathbf{M}$  6  $\mathbf{M}$  6  $\mathbf{M}$  6  $\mathbf{M}$  6  $\mathbf{M}$  6  $\mathbf{M}$  6  $\mathbf{M}$  8  $\mathbf{M}$  9  $\mathbf{M}$

技術に基づいた測定装置の試作機を完成させ、過剰キャリアによると思われる信号の深さ分 布の検出に成功した。

高耐圧化に対応する厚膜成長の開発においては、つくば拠点において  $250 \, \mu \, m$  成長のトライアイルを開始し、欠陥密度や、外形(ワレ・欠けの原因となりうるステップフローの上流での多形発生、後工程で問題となりうる外周部での異常成長(エピクラウン)、エピ後のそり)の現状確認を行っている。今後はシミュレーション技術も活用しながら厚膜成長における各種課題を解決していく。また、C 面成長においては  $250 \, \mu \, m$  の厚膜成長における課題抽出を行うことが最優先事項であり、そのための準備を進めている。現状において鏡面成長可能な成長プロセスウインドウの条件決定を急いでおり、現状では最大で  $36.7 \, \mu \, m/h$  まで確認した。今後、温度分布の均一性が高いウエハ配置への変更によって  $50 \, \mu \, m/h$  に近い成長速度での鏡面成長可能条件を決定して  $250 \, \mu \, m/h$  の厚膜成長のトライアルを実施しながら、超高耐圧デバイス用のエピウエハに求められるエピ濃度の低濃度化実現へと繋げていく。

一方、電中研拠点では、バイポーラの順方向特性劣化の発生状況を調べるためのPIN ダイオード用のエピタキシャル膜を作製し、つくば拠点に供給するとともに、放射光 X 線トポグラフィによる基底面転位密度の評価、時間分解フォトルミネッセンスによるキャリア寿命の評価を行った。また、産総研拠点、京大拠点と連携して、エピ成長におけるキャリア寿命の制御範囲を調査するとともに、窒素ドーピングによるエピウェハ形状の変化を明らかにした。また、つくば拠点では作成した PIN ダイオード TEG を使い電気特性に影響を及ぼす SiC エピウエハ欠陥の同定を行った。その結果、ウエハ欠陥の種類および存在箇所に応じて PN ダイオードの順方向特性および耐圧特性が低下することを確認した。今後引き続き、各拠点で連携し、ウエハ欠陥による PIN ダイオード特性低下要因解明を進める。

また、PN 接合界面形成やキラー欠陥の増加に影響が懸念されるドーピングによる格子歪みを微視領域で解析することを目的として電子線後方散乱回折(EBSD)法の有用性検討を開始した。今後、高分解能検出器により格子歪みの抽出や測定精度の改善を図るとともに、歪みが及ぼすデバイス性能への影響について考察を深める。

#### ②次世代 SiC デバイスの技術開発

## ②-(1) 新構造ユニポーラデバイス技術開発

平成26年度は、次年度以降のSJMOSFETのプロトタイプ試作を念頭に、6.5kVのSJ構造(SJドリフト層)の基本設計を行った。基本設計に際してはトレンチ加工精度、埋め戻しエピ濃度の制御性、イオン注入マスク加工精度などを考慮し、プロセスマージンを考慮したpnピラー幅、埋め戻し領域のエピ濃度およびpnピラー構造直下のバッファー層厚などを検討した。)の重要性を示す結果となった。またトレンチテーパー角に対する耐圧劣化の調査から、ドリフト層の高濃度化によりテーパー角増加に対する耐圧劣化が増大することを確認した。すなわち、低オン抵抗化には高濃度化が必須であるが、そのためにはテーパー角を垂直に近づけることが重要となる(現時点ではテーパー角度 $86.5^\circ$ 、深さ $50\square$ mのトレンチ形成を達成している。)トレンチ埋戻しエピ法によるSJ構造の形成では、成長温度、成長圧力、原料投入量、C/S比などの各種成長条件の詳細な検討に加え、塩素系の原料ガスおよびエッチングガス( $SiH_2Cl_2$ 、HCIなど)の導入効果、埋め戻しエピ成長途中でのエッチング工程導入効果について、トレンチ幅依存性を含めた系統的な検討を行った。結果として、目標値を大きく上回る、厚さ $10\mu$ m以上のボイドレス埋め戻しエピの見通しが立った。SJMOSFETの試作に向けて、MeVイオン注入マスクおよびSiCxエッチングマスク用の堆積膜形成装置を産総研つくば拠点に導入する準備を行った。

さらに筑波大とともに、SiC-SJデバイスの限界性能の追求を念頭に、Si-SJデバイスとのベンチマークを行い、6.5kVSJデバイス実現に向けて、目指すべき姿を明らかにした、筑波大ではSi C-SJデバイスの限界性能の追求を念頭に、SJドリフト層の微細化および高濃度化による耐圧-オン抵抗のトレードオフ向上の限界点に関する検討を開始する。

一方SiCゲート酸化膜界面連携体制に関しては、筑波大学を中心として、SiC酸化膜界面物理の学理解明に向け、SiC酸化膜に関する研究に参画する各機関(筑波大・産総研・阪大・東大・東北大)との連携体制を構築した。具体的には、本取り組みでの目標を共通化し、それを達成するために必要な評価項目を挙げ、評価に適した種々のTEGパターンを決定した。また、産総研に参画している企業のマネージャとも目標や進め方に対する議論を行い合意を得た。共通評価TEGパターンを用いたリソグラフィ用のマスク作成を完了させ、産総研におけるプロセス確認が進行中である。次年度から共通評価TEGチップの作成を行い、各機関に配布する。TEGが入手出来次第すぐに評価を開始できるよう、ストレス印加試験やEDMRなど各種測定環境のセットアップを進めている。

また阪大では、酸化膜SiC酸化膜界面の課題に関しては、酸化温度や雰囲気制御を従来の実験条件から大きく異なる幅広い条件にまで拡張するため、SiC加熱装置の設計開発ならびに学内クリーンルーム実験施設内での装置立上げを行い、装置検収を完了した。当該装置は高出力の赤外線ランプ加熱によってサセプタ上の小片試料の急速加熱が可能であり、2000℃以上の最高到達温度と急速加熱・急速冷却性能を確認した。本装置を用いて4H-SiC(0001) Si面のドライ酸化実験を1150℃から1600℃の広範囲の温度条件で実施し、分光エリプソメータにより決定した酸化膜厚から酸化速度を評価した。実施例が多い温度域(1150℃~1300℃)では、従来からの報告値に近い酸化速度が得られた。また、報告例が少ない1400℃以上のドライ酸化条件でさらに酸化速度が増大し、1600℃では数十秒で50nm程度の酸化膜が形成できることを確認した。現在、MOSキャパシタを作製して電気特性(C-V、I-V、界面準位密度)を評価中である。

## ②-(2) バイポーラデバイス技術開発

超高耐圧デバイスの実用化を考えた場合、低オン抵抗と低スイッチング損失の両立を図る必要がある。これまでに試作した IGBT のスイッチング特性としては、テール電流が温度を上げるとともに大きくなり、スイッチング損失が大きく増大した。この原因は、高温時において IGBT コレクタ側からのホール注入が大きくなり、またライフタイムの制御が不十分であることから、耐圧維持層内のコレクタ側キャリア分布が大きくなっているためと考えられる。本年度はオン特性とスイッチング特性の両立を目指した要素技術として、バイポーラデバイスのホール注入制御に関する検討を行った。具体的にはコレクタ側の電極構造及び層構成をシミュレーションにより最適化し、TEG (PiN ダイオードのカソード構造) 試作を行い、順方向特性を測ることにより、ホール注入制御方法の検証を行った。結果として、P++コンタクト領域の比率をコントロールすることにより、Vfを 100・200%の間で、コントロールできることが明らかとなった。

IGBT については、コレクタ側電極構造の検討を行い、Vf に及ぼす影響をシミュレーションと TEG 試作により検証を行っている。これまでに、ホール注入がより効果的にコントロールできる 構造を見出しつつある。また薄ウエハプロセスの検討を行い、問題点の把握と対策を進めている。 さらに自立エピ基板を作成し、透明基板の流動における問題の対策を進め、ライフタイムエンハンスメントを施したウエハを用いた素子の試作を開始できた。

京大においては、SiC バイポーラデバイスの見極めの一つとして、PiN ダイオードの究極的な

高性能化に取り組んでいる。まず、同じドーピング密度 $(2\times10^{14}~{\rm cm}^{-3})$ で、異なる厚さ $(約~50\sim270~{\rm \mu~m})$ を有する低濃度 n 型層(i 層)を有する SiC PiN ダイオードを作製し、その順方向特性を調べた。いずれも高温長時間熱酸化を施してi 層内ほぼ全域に亘って Z1/2 センターを低減した。i 層厚さ  $98\,\mu$  m $(14~{\rm kV}$  級)のダイオードで  $1.8~{\rm m}\,\Omega\,{\rm cm}^2$ 、厚さ  $148\,\mu$  m $(20~{\rm kV}$  級)のダイオードで  $4.0~{\rm m}\,\Omega\,{\rm cm}^2$ 、厚さ  $268\,\mu$  m $(35~{\rm kV}$  級)のダイオードで  $9.7~{\rm m}\,\Omega\,{\rm cm}^2$  という良好な微分オン抵抗を得た。また、これらの特性は、高注入状態におけるキャリア寿命が  $3\sim4\,\mu$  s として計算した解析結果と良い一致を示した。今後は、シミュレーションとの比較や温度依存性について調べる。

さらに SiC パワーデバイスのシミュレーションや設計に重要な衝突イオン化係数の精密決定に取り組んでいる。平成 26 年度は (i)従来(2.0~2.8 MV/cm)より低い電界範囲(1.0~2.0 MV/cm)、および(ii)より高い電界範囲(2.8~3.3 MV/cm)で SiC<0001>方向の衝突イオン化係数を求めた。前者は低濃度ドープ層を用いたパンチスルー構造、後者は高濃度ドープ層を用いたノンパンチスルー構造のフォトダイオードを作製し、光電流の増倍係数から衝突イオン化係数を算出した(図 2)。これにより特に 10~kV 超級の SiC デバイスの理論耐圧を正確に計算できるようになった。今後は、より広い温度範囲で衝突イオン係数を決定する予定である。

またウエハ Gr.との共通課題である、キャリア寿命制御に関しても、前述した、IGBT 試作ウエハのライフタイムエンハンスメントを実施した。

バイポーラデバイス、ユニポーラデバイス共通の問題である、順方向劣化に関しては、ウエハテーマ(高耐圧化対応技術開発)側と連携しながら、現状把握を行った。具体的には PiN ダイオード試作を行い、順方向劣化特性を計測し、順方向劣化現象の、電流密度依存性、トポ像、PL観察による解析などを進めており、その原因解明につながる知見が得られつつあるとともに、順方向劣化対策の指針が得られつつある。

#### ③次世代 SiC モジュールの技術開発

本研究開発課題では、モジュール技術の自動車分野への適用を視野に入れ、1.2kV級 SiC-MOSFET による高チップ電流密度  $(1kA/cm^2 \& M)$  モジュールの設計とその耐久性評価に関する技術を開発する。

高チップ電流密度化(1kA/cm²級)に対応するモジュールの実現には、高発熱密度となる SiC チップからの抜熱技術とともに、チップやチップ至近に配置する受動部品(ゲート回路の抵抗およびコンデンサ)の高温(250℃級)実装技術が要求される。このため、SiC チップ開発側との性能・仕様に関する情報交換と並行して、高耐熱部品(産総研中部センターを中心拠点)、耐高温接合(阪大産業科学研究所を中心拠点)、高温実装(産総研つくばセンターを中心拠点)の各側面から、適用可能な材料・要素技術の選定やその組合せ方法に関する調整を進めた。また、材料・要素技術の適用可否判断の観点からの評価試験を開始した。そして、SIP 内の別テーマである機電ー体形テーマを担当する芝浦工大との連携も図り、具体的アプリケーションからの要求仕様をモジュール設計に反映させた。本年度の具体的成果は、以下の通りである。

高温実装の検討では、参画応用機器企業とのモジュール仕様に関する議論を通じ、応用機器への適用の視点から空冷方式での高チップ電流密度 (1kA/cm²級) 化を図る方針を決定した。そして、この高電流密度形モジュールの実現に適用可能と考えられる材料および要素技術の選定を、高耐熱部品および耐高温接合の拠点と相互調整をとりながら進め、これに基づく 2 in 1 モジュールの基本構造設計を行った。設計したモジュールは、ワイヤボンド形と配線基板形の 2 種類である。(この基本構造に対して適用される技術の組合せ評価試験を 27~28 年度に実施し、その結果に基づいた適用技術の絞り込みを経て、最終設計を 28 年度に完了する計画である。)なお、この基

本構造の検討に際しては SIP 内で別課題を担当する芝浦工大での検討結果も取り込んでおり、機電一体形構造に対応するためのモジュール配置の制約(モジュールのフットプリント制限)や電流容量の要求仕様(定格 100Apeak、縁石乗り上げ時など苛酷条件時には 200A-3 秒に対応)を考慮に入れた設計となっている。

モジュールの基礎構造が決まった事から、モジュールに使用する材料や部品の設計具体化とともに、性能評価試験法の検討も進めた。今年度は、試作モジュールに適用する材料・技術の絞り込みの目的で 27~28 年度に実施する材料および要素技術の組合せ評価試験の方法(試験サンプルの設計と、これを用いた試験の条件)を検討した。

高耐熱部品の検討では、高温実装拠点ならびに共同実施先である東大(宮山研究室)、東工大 (鶴見研究室)との連携体制の下、部品の単体評価試験法を決定した。また東工大(鶴見研究室) では、コンデンサの耐性・信頼性に関する基盤研究(誘電体の絶縁機構)に関し、部品メーカと の協力の下、誘電体材料の絶縁破壊強度や誘電率の温度依存性の評価検討を開始した。東大(宮 山研究室)では、抵抗体の耐性・信頼性に関する基盤研究(抵抗体の導電機構)に関し、抵抗体 の局所反射率測定法の定量性精度や空間分解能の確認、精密評価のための材料表面処理法等を検 討し、その有効性確認を行った。これらの材料評価の知見は、部品仕様に反映させるため高耐熱 部品拠点で共有した。

耐高温接合の検討では、接合材料の要素評価試験および組合せ評価試験について、モジュール構造設計を行う高温実装拠点との連携の下で試験条件等の調整を図り、評価方法を決定した。そして、Ag 系接合の要素評価試験を開始した。

高温実装の検討では、共同実施先の東大(泉研究室)と連携して、モジュールの基礎設計の確認を目的とした要素構造等の組合世評価試験について、高耐熱部品や耐高温接合拠点との相互調整を経た上で、試験方法を決定した。なお、東大(泉研究室)は、機械歪みの SiC チップ特性への影響の観点から、機械的側面を中心に知見を提供した。特に、組合せ状態での耐久性の評価に関しては、応用機器側からの要望と開発期間を考慮した調整を重点的に行い、高温保持(250℃-1,000h)、温度サイクル(-40℃~+250℃-1,000回)、パワーサイクル(30,000回)による評価から、実用化への基礎データ取得を行う事を決定した。また、樹脂に関しては、モジュールを構成する全ての材料・部品と接触する事から、その密着性を評価するための組合せ評価試験が優先順位の高い項目との結論に至り、試験サンプルの構造と、試験条件(高温保持試験の温度および時間、接合強度などの接合の評価方法など)を決定した。(上記の基礎構造に基づいて決定されたこれらの評価試験については、一部は本年度に開始しているが、本格的な開始は 27 年度からとなる。)

また、高電流密度( $1kA/cm^2$ 級)化とそれに伴う高発熱密度化に対応するために必要な設計技術の高度化を目的に、設計の基礎データとなるモジュールを構成する材料・部品の低温から高温域における熱的物性(熱伝導率、比熱)および機械的物性(線膨張率、ヤング率、強度等)に関しても、高耐熱部品、耐高温接合、高温実装を担当する各グループ間で試験方法や取得データ内容の調整を行い、試験サンプルの設計と試験方法・条件を決定した。そして、高耐熱部品拠点におけるセラミックの線膨張率の温度特性( $-50\sim+400$ °C)測定の結果からは、これまでの解析では必ずしも考慮できていなかった物性値の温度依存性を明らかにした。この知見は、高温実装や耐高温接合に提供され、組立プロセス中の経験温度履歴に起因する材料挙動を考慮可能とした。

耐高温接合技術に関しては、250℃常用にも対応可能な接続および配線の確立を目的に、阪大産業科学研究所において Ag 焼結法による低温・低加圧プロセスによる接合形成技術の開発に取り組んだ。高温環境下では、材料自身の劣化だけでなく、周辺材料との化学的・冶金工学的反応の

進行も懸念されることから、SiC 半導体チップと Ag 接合材の組み合わせ試験サンプルを利用した高温保持試験(200 および 250 $^{\circ}$ Cで、150 および 300 時間の 4 条件での試験)を行い、チップ電極部分などの熱による劣化進行を調べた。その結果、Ag と Ni の界面において Ni 拡散に起因すると考えられる劣化の進行を確認した。この現象は、セラミック基板の導体層における Ni めっき面でも起こる懸念があるため、その機構解明や劣化の進行速度の把握に向けた試験を、接合強度評価と並行して実施することとなった。また、産総研つくばセンターでは、Cu-Sn 系 TLPS(遷移的液相焼結)接合の接合界面分析の結果から、接合強度や熱的特性に改善余地があることを解明した。この結果を受け、特性向上を図る観点から、材料組成の改良と接合形成条件の最適化に向けた試験を行う事となった。

- 2. 成果(当該年度分についてのみ記載)

- (1) 研究発表・講演 (口頭発表も含む) 無し

- (2) 特許等 無し

- (3) 受賞実績 無し

- 3. その他特記事項(当該年度分についてのみ記載)

- (1) 成果普及の努力 (プレス発表等) 無し

- (2) その他 無し

契約管理番号 14101669-0

開発項目 「SIP(戦略的イノベーション創造プログラム)/次世代パワーエレクトロニクス/SiCに関する拠点型共通基盤技術開発/ハイブリッド自動車向けSiC耐熱モジュール実装技術の研究開発」 平成26年度~平成28年度のうち平成26年度分中間年報

委託先名:学校法人早稲田大学

国立大学法人九州工業大学

トヨタ自動車株式会社

株式会社デンソー

# 1. 研究開発の内容及び成果等

- (1) 1. HV向けSiC耐熱モジュール実装の構想・企画・研究開発マネジメント 耐熱モジュール最適化構造に関する特許案を作成し、出願準備中。

- (2) 革新技術の研究開発

- ①高耐熱チップ導電接続技術開発・3次元化接続基礎技術

# <u>・ナノニッケルを利用した耐熱接合技術</u>

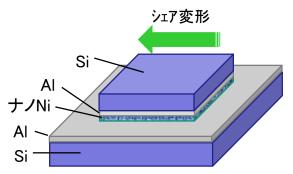

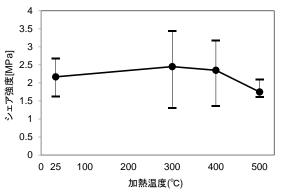

ナノニッケルを利用した耐熱接合において 300℃の接合温度で数 MPa に達する接合強度を実現し、さらなる高温保持でも大きな強度低下が無いことを確認した。

図1. 接合強度評価に用いた接合 部材(Si ダミーチップをナノ Ni で

図2.シェアテストで得られた接合 強度と接合後の加熱温度の関係

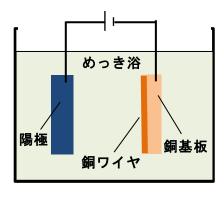

### ・銅ワイヤを介しためっき接合基礎技術

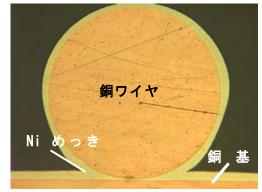

銅ワイヤを介しためっき接合基礎技術を開発し、めっき条件の制御により接合強度制御を可能 とした。また接合界面の性状を電子散乱法や表面分析手法で解析し結晶配向、元素分布などを 明らかにした。

図3. 銅ワイヤのめっき接合方法

図4. Ni めっきで接合した銅ワイヤ/基板の接合界面性状

# ・パッケージへの耐熱実装基礎技術

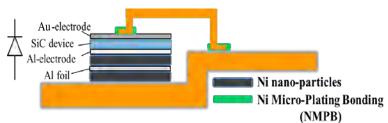

ナノ金属接合、応力緩和接合機構 、めっき接合技術などを総合的に活 用し図5に示すような SiC ショット キーバリアダイオードの耐熱実装を 実現。300℃での整流動作を確認 し H26 年度目標を達成した。本技術 を基礎技術とし H27 年度以降の開発に 取り組む予定。

図 5 . SiC-SBD のナノ Ni 接合およびめっきで接合によるパッケージへの実装

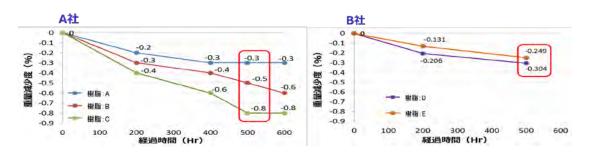

②絶縁材料の高耐熱、高熱伝導化、高絶縁化(三井ハイテック殿) H26 年度目標:重量減少度 0.5%以下(200℃×500Hr)の樹脂選定

# ◇重量減少度/密着性評価結果

| 樹脂 | 500Hr 重量<br>減少度(%) | RT密着強度<br>(MPa) | 200℃密着<br>強度(MPa) | 250℃密着<br>強度(MPa) | 密着強度減少率<br>※(%) |

|----|--------------------|-----------------|-------------------|-------------------|-----------------|

| А  | 0.3                | 15.3            | 7.8               | 1.9               | 87.6            |

| В  | 0.5                | 10.7            | 7.4               | 4.2               | 60.7            |

| С  | 0.8                | 4.3             | 3.3               | 2.7               | 37.2            |

| D  | 0.30               | 9.26            | 1.69              | 0.85              | 90.8            |

| E  | 0.25               | 8.08            | 4.19              | 2.05              | 74.6            |

図6. 耐熱樹脂の評価試験結果の一部(上段)および比較結果(下段)

上記樹脂メーカーによる評価の結果、4種の樹脂にて重量減少率 0.5%以下である事が確認出来た(図 6)。平行してMHTによる検証を含めた同様の評価を実施する予定。H27年度 5月末までに検証実験を実施予定。

③革新技術の標準パッケージ、試作・評価・検証(三井ハイテック、ウォルツ)

H26 年度目標:200℃環境下での動作確認

「発熱チップ裏面とダイバットのめっき接合」及び「 $2.7\sim7.5 \,\mathrm{mm}\,\mathrm{S}$  i  $\mathrm{C}$  チップのめっき接合」に関しては、リードフレームを作製し試作評価中。懸案事項だった「チップ側面へのめっき付着」に関しては、めっき前にチップ側面をマスキング樹脂でコーティングする事で、山形部に大きな影響も無く、めっき接続できる事を確認。また「 $3\,\mathrm{D}$  めっき接合」に関しては構造を検討中。 $\mathrm{H26}$  年度目標の  $200\,\mathrm{C}$ 環境下での動作確認については概ね達成見込みであり、 $\mathrm{H27}$  年度  $7\,\mathrm{月末}$ までに検証実験を実施予定。

また既存の温度センサー付き発熱 TEG を元にさらに高温に発熱する TEG の開発を行った。 既存 TEG 発熱体はチップ内で局所的に発熱しているため、チップ全体での発熱効率が悪い。 そこで、チップ内での熱抵抗の低いメタルを全面に配置し、チップ全面より効率よく発熱さ せることで更なる高温化を目指した。実チップの作製のために、既存製品のメタル層とパッシベーション層を修正し、現在、図面チェックを実施中。

#### (3) 自動車応用の研究開発

①HV向けSiC耐熱モジュール最適化基礎検討(九州工業大学/FAIS)

SiC 耐熱モジュール最適化基礎検討として、試作パワーモジュール 3 次元構造を考案し、そのモデル化を行った。モジュールの寄生インダクタンスのシミュレーションを行う環境を整備し、寄生インダクタンスの評価を開始した。すなわち、シミュレーションソフトウエアとして、高周波電磁界解析 (ANSYS 社; Q3D) および回路解析ソフトウエア (ANSYS 社; Simplore)を導入し、回路のサージ解析を可能とした。さらに、実験による寄生インダクタンス推定を行うべく、1200V 耐圧の SiC-MOSFET および SiC-SBD を用いた試作パワーモジュール評価用のインバータ回路(制御回路、電源回路、ゲート駆動回路、電流検出回路を含む)を設計・製作し、回路動作を確認した。パワーモジュールのパワーサイクル試験評価用の試験装置の検討・手配を行った。また、 他機関のパワーモジュールの設計調査を行った。

#### (4) その他

HV向けSiC耐熱モジュール実装の構想および革新技術の材料選定に関して、車両搭載の観点から、技術課題、製造工程上の制約条件、評価条件、目標値等についての助言、情報提供を行った。来年度の評価、実験に必要なSiC素子(ダミー品)の供給について、供給数、供給時期に関して検討する。(デンソー)

#### 2. 成果

(1) 研究発表・講演 (口頭発表も含む)

なし

(2) 特許等

なし(出願検討中)

(3) 受賞実績

なし

- 3. その他特記事項(当該年度分についてのみ記載)

- (1) 成果普及の努力 (プレス発表等)

SiC 関連技術の成果普及のためオール SiC カーのプレスリリースを行った。(トヨタ自動車) ナノ接合技術の一部は国際会議などでの発表を計画中。また北九州地区で本研究成果含む研究会を企画予定で成果を PR するとともに幅広く当該技術の研究者を招き討論を行う予定。

# トヨタ自動車、

# 新素材 SiC パワー半導体搭載車両の公道走行を開始

- カムリの PCU、燃料電池バスの昇圧コンバーターに搭載。燃費向上効果を検証 -

トヨタ自動車(株)(以下、トヨタ)は、SiC パワー半導体\*1の実用化に向けた取り組みの一環として、ハイブリッド車(以下、HV)などのモーター駆動力を制御するパワーコントロールユニット(以下、PCU)に新素材 SiC パワー半導体を搭載したカムリ(HV)の試作車を開発し、2015年2月初めより約1年間、豊田市を中心に公道での走行試験を行う。

<PCUに新素材 SiC パワー半導体を搭載したカムリ試作車(左)、PCU(右)>

<FC バス>

PCU は、走行時はバッテリーの電力をモーターに供給、減速時は回生した電力をバッテリーに充電するなど、HV などの電力利用において重要な役割を担っている。その PCU に使われているパワー半導体は、車両全体の電力損失の約 20%を占めており、パワー半導体の高効率化、すなわち、電流を流す時の抵抗を低減することが燃費向上に不可欠である。

今回開発したカムリ試作車は、PCU 内の昇圧コンバーターおよびモーター制御用インバーターに、SiC パワー半導体(トランジスタ、ダイオード)を搭載している。

公道走行試験では、走行速度や走行パターン(高速走行、市街地走行、渋滞等)、外気温など様々な 走行条件毎に、PCU内の電流、電圧などのデータを取得し、現状のシリコン半導体と比べ、新素材である SiCパワー半導体搭載による燃費向上効果を検証していく。

さらに、2015 年 1 月 9 日から、豊田市内の路線バス (とよたおいでんバス「豊田東環状線」)として営業運行している燃料電池バス (FC バス) においても、FC スタックの電圧を制御する FC 昇圧コンバーターに SiC ダイオードを搭載しており、走行データを取得し、燃費向上効果を検証する。

なお、今回、カムリ試作車と FC バスに搭載した SiC パワー半導体は、国家プロジェクト\*2の成果の一部である高品質な SiC ウェーハ技術を採用している。

トヨタは、HV など電動車両の燃費向上において、エンジンや空力性能などの改善はもとより、パワー 半導体の高効率化も重要技術として位置づけており、新素材 SiC パワー半導体の早期実用化に向けて、 公道走行データを開発に反映していく。

- \*1 SiC は、<u>Si</u>licon <u>C</u>arbide の略。シリコンと炭素の化合物。 SiC パワー半導体は、トヨタ、(株) デンソー、(株) 豊田中央研究所と共同で開発。

- \*2 低炭素社会を実現する新材料パワー半導体プロジェクト。独立行政法人「新エネルギー・産業技術総合開発機構」 (NEDO) の委託で、技術研究組合「次世代パワーエレクトロニクス研究開発機構」(FUPET) が実施。

以上

# **Toyota to Trial New SiC Power Semiconductor Technology**

Toyota City, Japan, January 29, 2015—Using a "Camry" hybrid prototype and a fuel cell bus, Toyota Motor Corporation will bring a brand new technology to the streets of Japan for testing this year. The tests will evaluate the performance of silicon carbide (SiC) power semiconductors, which could lead to significant efficiency improvements in hybrids and other vehicles with electric powertrains.

Camry prototype (left) and fuel cell bus (center) featuring SiC power semiconductors; power control unit

# **Technology**

Power semiconductors are found in power control units (PCUs), which are used to control motor drive power in hybrids and other vehicles with electric powertrains. PCUs play a crucial role in the use of electricity, supplying battery power to the motors during operation and recharging the battery using energy recovered during deceleration.

At present, power semiconductors account for approximately 20 percent of a vehicle's total electrical losses, meaning that raising the efficiency of the power semiconductors is a promising way to increase powertrain efficiency.

By comparison with existing silicon power semiconductors, the newly developed high quality silicon carbide (SiC) power semiconductors create less resistance when electricity flows through them. The technologies behind these SiC power semiconductors were developed jointly by Toyota, Denso Corporation, and Toyota Central R&D Labs., Inc. as part of the results of a broader R&D project in Japan.

#### Test vehicles and period

In the Camry hybrid prototype, Toyota is installing SiC power semiconductors (transistors and diodes) in the PCU's internal voltage step-up converter and the inverter that controls the motor. Data gathered will include PCU voltage and current as well as driving speeds, driving patterns, and conditions such as outside temperature. By comparing this information with data from silicon semiconductors currently in use, Toyota will assess the improvement to efficiency achieved by the new SiC power semiconductors. Road testing of the Camry prototype will begin (primarily in Toyota City) in early February 2015, and will continue for about one year.

Similarly, on January 9, 2015, Toyota began collecting operating data from a fuel cell bus currently in regular commercial operation in Toyota City. The bus features SiC diodes in the fuel cell voltage step-up converter, which is used to control the voltage of electricity from the fuel cell stack.

Data from testing will be reflected in development, with the goal of putting the new SiC power semiconductors into practical use as soon as possible.

<sup>\*</sup>Conducted by the R&D Partnership for Future Power Electronics Technology under consignment from the New Energy and Industrial Technology Development Organization.

| 契約管理番号 | 1 4 1 0 1 6 7 3 - 0 |

|--------|---------------------|

|        | 1 4 1 0 1 6 7 4 - 0 |

|        | 1 4 1 0 1 6 7 5 - 0 |

|        | 14101676-0          |