#### 資料 2

重要技術領域検討ワーキンググループ (第4回) 2025.10.2

### 先端ロジック半導体の最新動向

### 平本俊郎 東京大学生産技術研究所 hiramoto@nano.iis.u-tokyo.ac.jp

- 1. はじめに:半導体を取り巻く状況

- 2. ロジック半導体デバイスのトレンド

- 3. 技術ノードとは?

- 4. ロードマップによる将来予測

- 5. 3D^

- 6. まとめ

# 半導体を取り巻く世界の状況(1)

| 年    | 月  | 半導体の動き                                                 |  |  |

|------|----|--------------------------------------------------------|--|--|

| 2017 |    | 半導体産業,空前の好景気.                                          |  |  |

| 2018 |    | 米中半導体戦争.                                               |  |  |

| 2019 |    | メモリ不況.                                                 |  |  |

| 2020 |    | コロナ禍,半導体特需,半導体不足.                                      |  |  |

|      |    | 日本の装置・材料メーカーの強さ。                                       |  |  |

| 2021 | 3  | Post 5Gプロジェクト,420億円,東京エレクトロン,キヤノン,SCREEN.              |  |  |

|      | 6  | 半導体・デジタル産業戦略を発表。                                       |  |  |

|      | 10 | TSMC・ソニーが合弁で熊本に半導体新工場,22-28nm技術。                       |  |  |

|      | 12 | 半導体市場予測,1兆ドル産業へ。                                       |  |  |

| 2022 | 2  | TSMCの熊本工場,1兆円に拡大,12-16nm技術。                            |  |  |

|      | 11 | 新会社Rapidus,国内で2nm半導体を量産へ。補助金700億円,                     |  |  |

|      | 12 | LSTC (Leading-edge Semiconductor Technology Center)設立. |  |  |

|      | 12 | RapidusがIBMと連携.                                        |  |  |

|      | 12 | TSMC,米国で先端半導体3nmを生産,投資は5.5兆円。                          |  |  |

# 半導体を取り巻く世界の状況(2)

| 年    | 月  | 半導体の動き                        |  |  |

|------|----|-------------------------------|--|--|

| 2023 | 2  | Rapidusの工場は北海道千歳市.            |  |  |

|      | 4  | Rapidus, ベルギーのimecと連携.        |  |  |

|      | 6  | 半導体・デジタル産業戦略を改訂。              |  |  |

|      | 6  | 米国、半導体の対中国規制、拡大。              |  |  |

|      | 11 | 半導体や生成AI. 補正予算, 2兆円.          |  |  |

| 2024 | 2  | LSTC, Beyond 2nm開発を開始.        |  |  |

|      | 4  | Rapidusへ追加支援,経産省,5900億円,後工程も。 |  |  |

|      | 4  | TSMC最高益,AI活況,スマホから主役交代。       |  |  |

|      | 6  | NVIDIA時価総額,世界首位,GAFAから主役交代.   |  |  |

|      | 12 | インテル,ゲルシンガーCEOが退任,業績低迷.       |  |  |

|      | 12 | TSMC熊本工場が量産開始。                |  |  |

| 2025 | 4  | Rapidus,試作を開始,2ナノ半導体.         |  |  |

|      | 7  | Rapidus,2ナノ半導体の試作品を初公開。       |  |  |

|      | 9  | NVIDIAがインテルに7400億円出資。         |  |  |

先端半導体 = 3nmのロジック半導体?

先端ロジック半導体と呼ぶべき

ロジック半導体とは? 3nmとは?

### 富岳:スーパーコンピュータ

### the japan times

https://www.japantimes.co.jp/news/2020/07/04/national/science-health/japan-fugaku-supercomputer-coronavirus-drugs/

Japan's Fugaku supercomputer, world's fastest, narrows down COVID-19

drug candidates

JIJI, KYODO

Ranked #1 in TOP500 in June, 2020.

https://www.top500.org/lists/top500/2020/06/

158,976 CPUs CPU (Fujitsu): Armv8.2-A SVE 512bit 48 Cores 7nm FinFET (TSMC)

Source: RIKEN

https://www.r-ccs.riken.jp/jp/outreach/photogallery.html

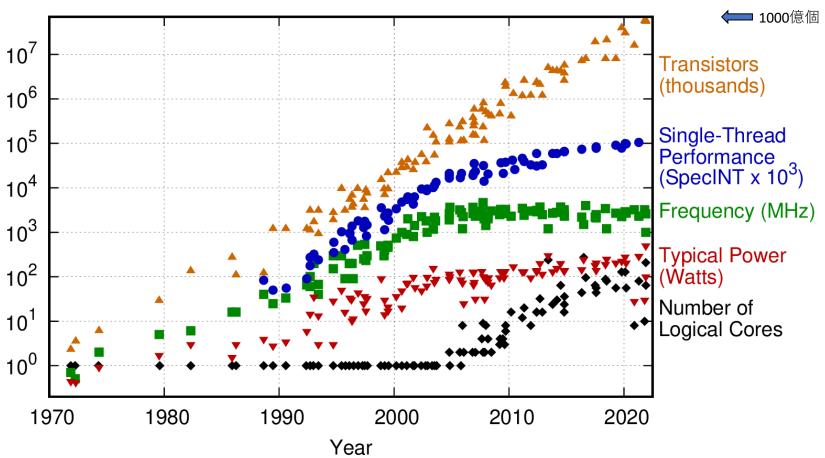

### 50 Years of Microprocessor Trend Data

Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten New plot and data collected for 2010-2021 by K. Rupp

https://github.com/karlrupp/microprocessor-trend-data?tab=readme-ov-file

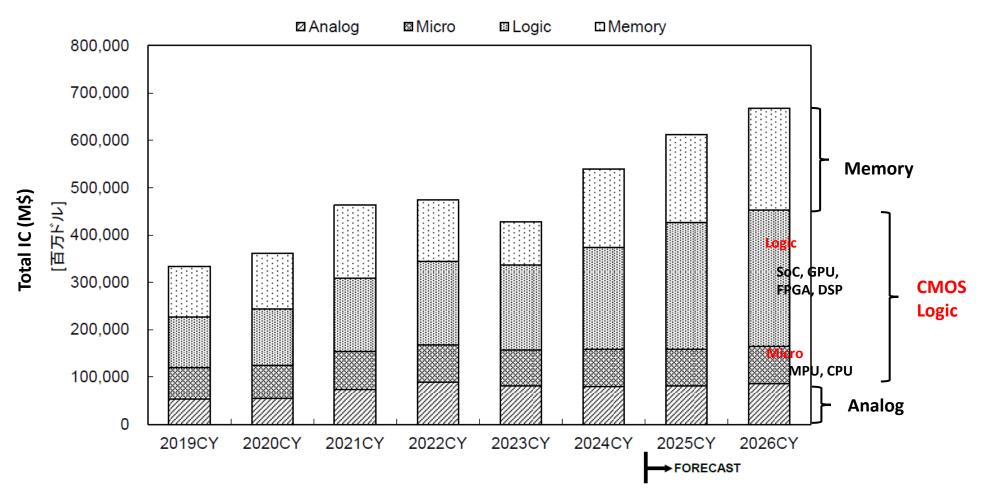

### 半導体市場:ICトータル

WSTS (WORLD SEMICONDUCTOR TRADE STATISTICS) https://www.jeita.or.jp/japanese/stat/wsts/docs/20250603WSTS.pdf

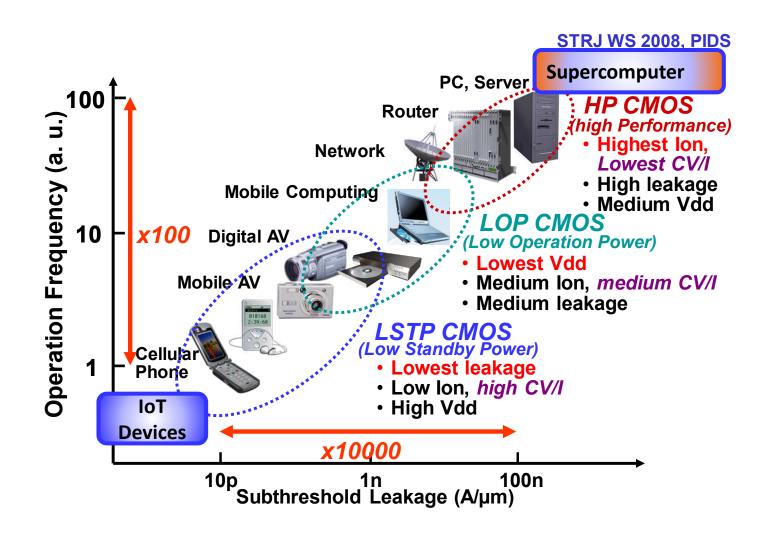

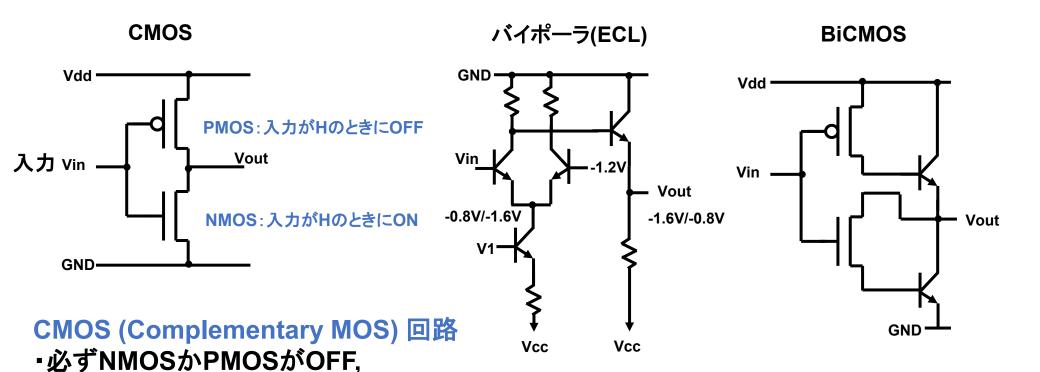

### メモリとの違いは?

メモリは種類が多い ロジックはほぼCMOSのみ

### ロジック回路の比較

定常的に電流が流れない

・ 直列と並列を組み合わせると演算が可能

・ほぼすべてのIT機器に利用されている

9

### なぜCMOSのみが生き残ったか?

スケーラビリティ

# なぜ微細化するか? スケーリング則 \*\* THE UNIVERSITY OF TOKYO

| トランジスタ寸法 L, W<br>膜厚 tox<br>接合深さ xj<br>空乏層幅 Wd<br>基板不純物濃度 Na<br>電源電圧 Vdd | 1/k<br>1/k<br>1/k<br>1/k<br>k<br>1/k  | 空乏層 シリサイド ゲート酸化膜 STI アース n+ STI n+ STI  |

|-------------------------------------------------------------------------|---------------------------------------|-----------------------------------------|

| 電流 Id<br>容量 C<br>遅延時間 t = CV/I<br>消費電力 P = IV                           | 1/k<br>1/k<br>1/k<br>1/k <sup>2</sup> | サース<br>シリサイド<br>グート 歌化類<br>Si substrate |

| トランジスタ数                                                                 | $k^2$                                 |                                         |

微細化 > 高速化, 低消費電力化, 高集積化を同時に達成! さらにコスト低減も!

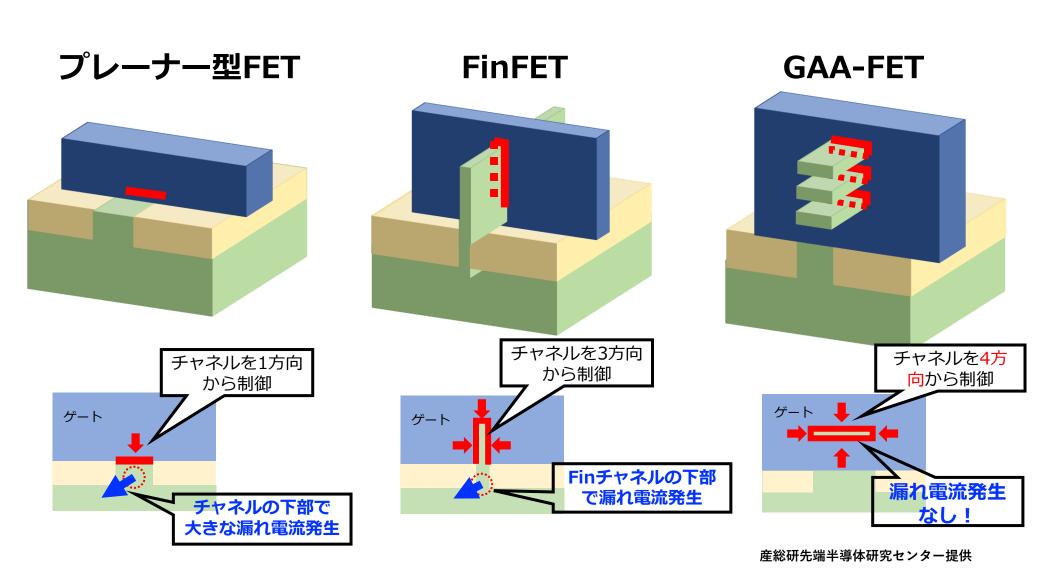

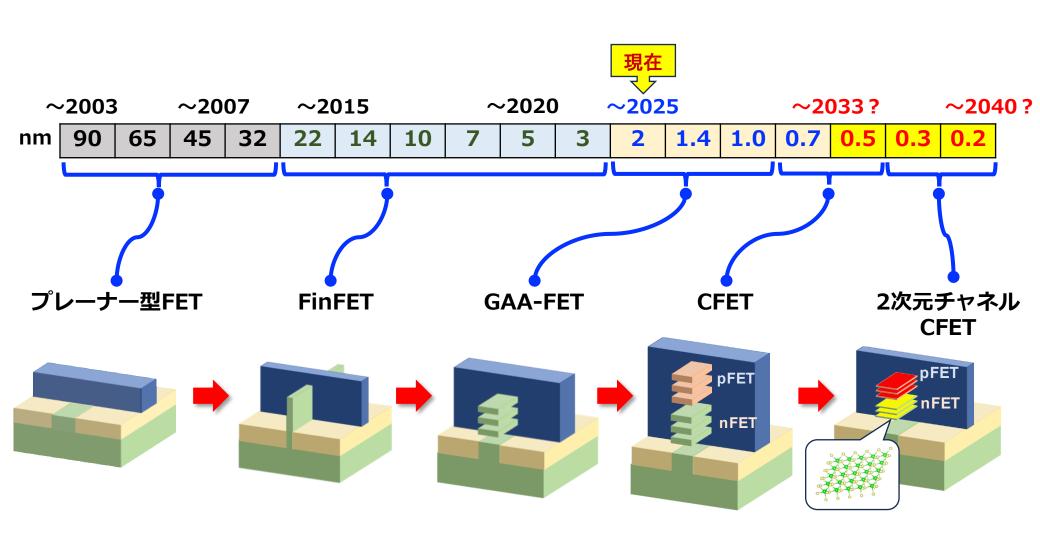

### MOSFETの構造が変化している

プレーナー構造 → FinFET → GAA → CFET

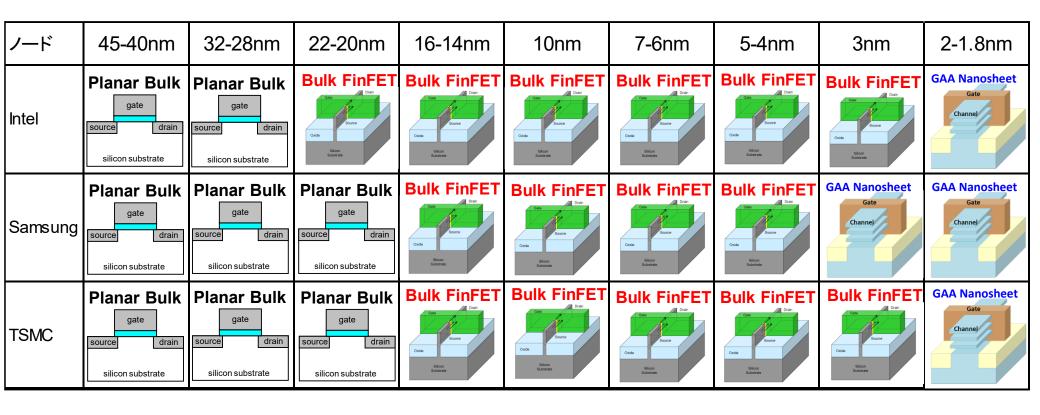

# CMOSデバイス構造の変化

13

# CMOSデバイス構造の変遷

日本企業 Rapidus SMIC

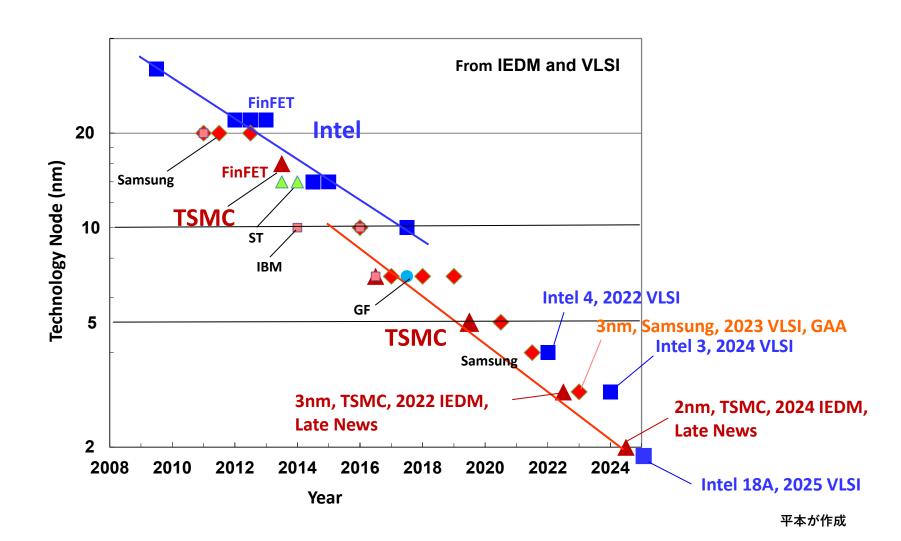

# CMOSプラットフォーム論文

2nm技術において, いったいチップ上のどこが2nmなのか? 2nmノード, 2nmプロセス, 2nm世代, 2nm設計ルール, 回路線幅2nm

ゲート長? 線幅(配線幅)?

2nm世代チップにおいて、2nmの箇所はどこにもない.

[1] L. C. Parillo et al., IEDM, p. 706, 1980. [2] L. C. Parillo et al., IEDM, p. 752, 1982. [3] J. Agraz-Guerena et al., IEDM, p. 63, 1984. [4] R. A. Chapman et al., IEDM, p. 362, 1987. [5] J. Hayden et al., IEDM, p. 417, 1989. [6] R. A. Chapman et al., IEDM, p. 101, 1991. [7] M. Bohr et al., IEDM, p. 273, 1994. [8] M. Bohr et al., IEDM, p. 847, 1996. [9] S. Yang et al., IEDM, p. 197, 1998. [10] S. Tyagi et al., IEDM, p. 567, 2000. [11] S. Thompson et al., IEDM, p. 61, 2002. [12] P. Bai et al., IEDM, p. 657, 2004. [13] K. Mistry et al., IEDM, p. 247, 2007. [14] S. Natarajan et al., IEDM, p. 941, 2008. [15] C. Auth et al., VLSI, p. 131, 2012. [16] S. Natarajan et al., IEDM, p. 71, 2014. [17] C. Auth et al., IEDM, p. 673, 2017. [18] M. Clinton et al. ISSCC, p. 210, 2017. [19] G. Yeap et al., IEDM, p. 879, 2019. [20] Y. Wang, IEDM, 2022. [21] G. Yeap et al., IEDM, 2024. [22] K. Fischer et al., VLSI, T1.1, 2025.

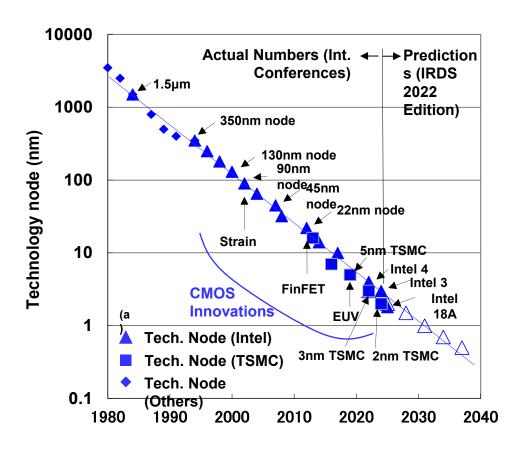

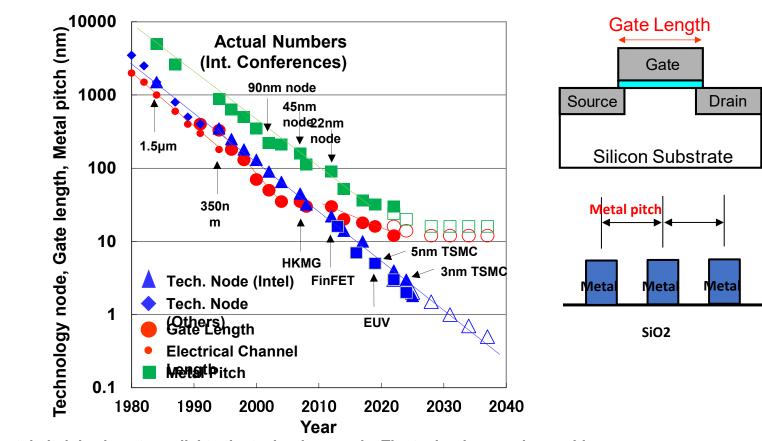

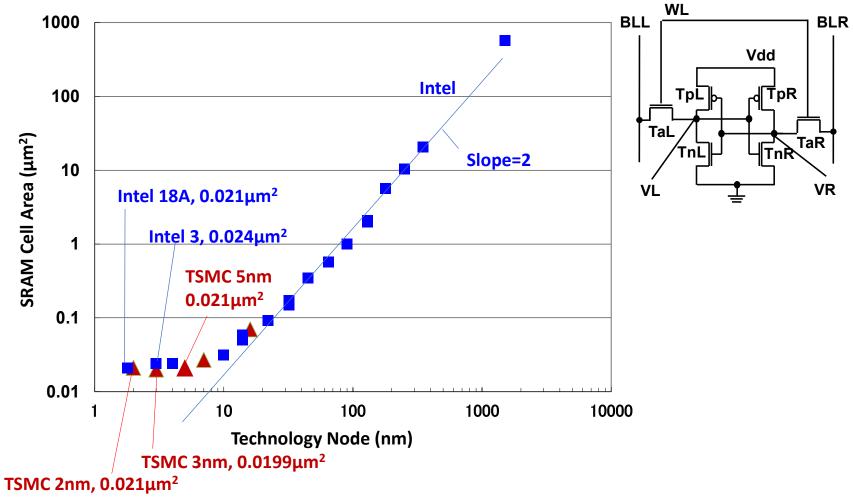

The metal pitch is almost parallel to the technology node. The technology node roughly reflects the integration density of transistors. How about SRAM? Cell Area  $\sim (Node)^2$ ?

T. Hiramoto, IEEE SNW, 2024 にデータを追加

## SRAMセル面積

- 0.35µmくらいまでは技術ノードはゲート長と一致していた.

- その後, 技術ノードはゲート長ではなくなり. 集積密度をほぼ表していた.

- ところが、最近は明らかに技術ノードの数字が小さすぎる. 実際には技術ノードの数字ほどには集積密度は高くない.

- ファウンドリほど数字を小さく言いたがる.

- 要するに技術ノードとは、製品名のようなもの、ノードの数字と同じ寸法に設計 されている個所はチップ上には存在しない。

- 平面的ではなく、立体的に集積しても集積密度は上がるので、3D集積すれば 技術ノードの数字を小さくできる。

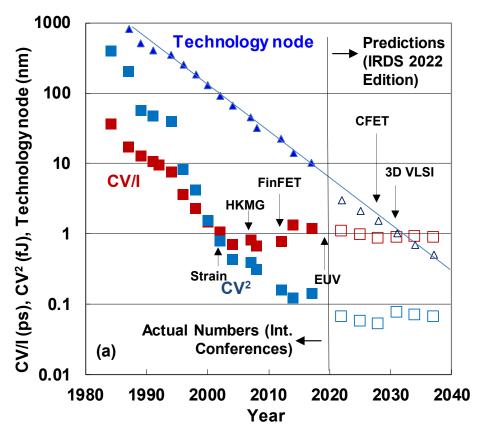

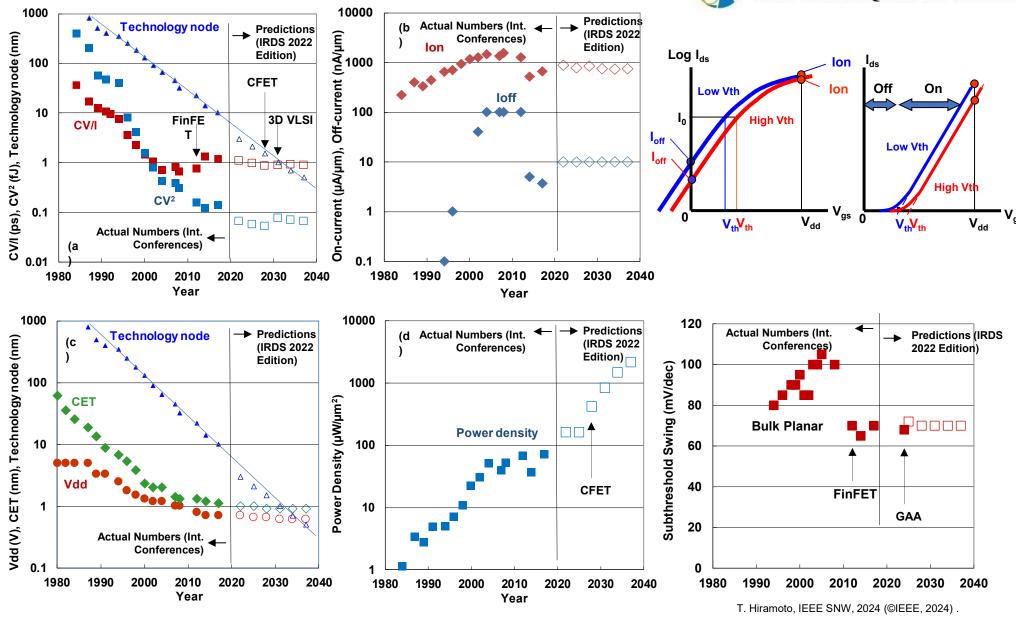

## 速度とエネルギー

観測: 速度とエネルギーは急速に改善してきたが、

最近では飽和傾向にある.

進歩は緩やかになっている。

理由: 寄生抵抗と寄生容量,Vdd, Tinv, Vthが

限界に近付いている.

注意: 速度とエネルギーはトレードオフの関係にある.

たった一つの技術で「大ジャンプ」は

過去にはなかった.

Assumption: (1) The gate width W=10Lg in planar transistors, (2) fin number reduced from 3 (2012) to 1 (2024), (3) GAA stacked sheet number increased from 3 (2025) to 4 (2031), (4) CFET introduced in 2028, (5) stacked tier number increased from 2 (2031) to 6 (2037), (6) FO=1, and (7) Ion and loff are normalized to effective width (Weff).

# THE UNIVERSITY OF TOKYO

## 以上からわかること

- CV/IおよびCV<sup>2</sup>によると、デバイス単体の性能向上は飽和傾向にあるが、 集積密度が上がるためシステム性能は依然として向上しコストは下がる。

- 過去には1つの技術による「大ジャンプ」はなかった. 指数関数的な進歩を 続けるには、新技術を継続的に導入していく必要がある.

- 電源電圧を下げることは低消費電力化のために必須.

- 旺盛な半導体需要に支えられて集積密度向上は必ず進むと予想される。 緩やかな配線ピッチ微細化および3次元化。

- 従来の延長線上にない新デバイス(急峻スロープトランジスタ等)の導入が 待たれるが、実用化の見通しはまだたっていない。 市場はむしろ従来デバイスの各段の性能向上を求めている。

- 市場からの要求を考慮すると、ノイマン型コンピューティングからの脱却は 難しい?

- 量子計算などの新アーキテクチャとの融合.

### ロードマップ

産総研先端半導体研究センター提供

- 1. 我が国は半導体復権にむけて動き出した. Rapidusに期待.

- 2. 生成AI等の爆発的普及でロジック性能向上への要請は非常に強い.

- 3. CMOSイノベーションは続く、デバイス性能向上のスピードは以前ほどではないが、 旺盛な需要に支えられて、確実に進歩は続く。

- 4. 先端CMOSはナノの1桁台に突入したが、実は技術ノードの数字ほどに微細化は 進んでいない. デバイスサイズ以外の総合力で性能向上を維持.

- 5. CMOSは3次元へ. 新材料の導入も続く.

- 6. さまざまな市場の要求に応えるため, 劇的な高速性と低消費電力化が必須.

- 7. さまざまなアーキテクチャ,新デバイスがCMOS性能を補完していく.